linux vcs是編譯型verilog模擬器,是一種用來進行模擬看波形的工具;其類似windows下面的modelsim以及questasim等工具,以及quartus、vivado模擬的操作。

本教學操作環境:linux5.9.8系統、Dell G3電腦。

linux vcs是什麼?

VCS工具的基本使用

VCS是在linux下面用來進行模擬看波形的工具,類似windows下面的modelsim以及questasim等工具,以及quartus、vivado模擬的操作。

vcs的常見指令後綴

| 指令 | 含義 |

|---|---|

-l readme.log |

用於將編譯產生的信息放在log檔內 |

v2k |

是讓VCS相容verilog 2001以前的標準 |

-debug_all |

用於產生debug所需的檔案 |

#-f verilog_file.f |

|

|

|

|

|

| #可將.f檔案裡的原始碼全部編譯-R |

./simv |

|

#原始檔有修改時,只重新編譯有改動的**.v* *文件,節省編譯時間。 |

-sverilog打開對Systemverilog | 的支持,編譯

-timescale=1ns/1ns

| ##-o simv_file | |

|---|---|

,可以使用-o 來變更執行檔名。如果這裡修改執行模擬時候就不是使用 | simv而是對應的o名字了。 |

|

採用的是全加器的官方教學,首先介紹不使用腳本的執行過程。

(1)先執行vcs加入對應的full_adder檔案

vcs -sverilog -debug_all -timescale=1ns/1ps full_adder.v full_adder_tb.v -l com.log

這裡先寫full_adder.v 是因為 tb檔案需要呼叫它,所以先把被呼叫的檔案寫出來,這條語句會產生simv檔案(如果使用了-o simv_file會產生對應的檔案名稱)。

(2)可以用./simv檔案執行波形的介面,也可以採用下面指令以後台方式開啟一個介面。

dve &或者 ./simv -l run.log -gui

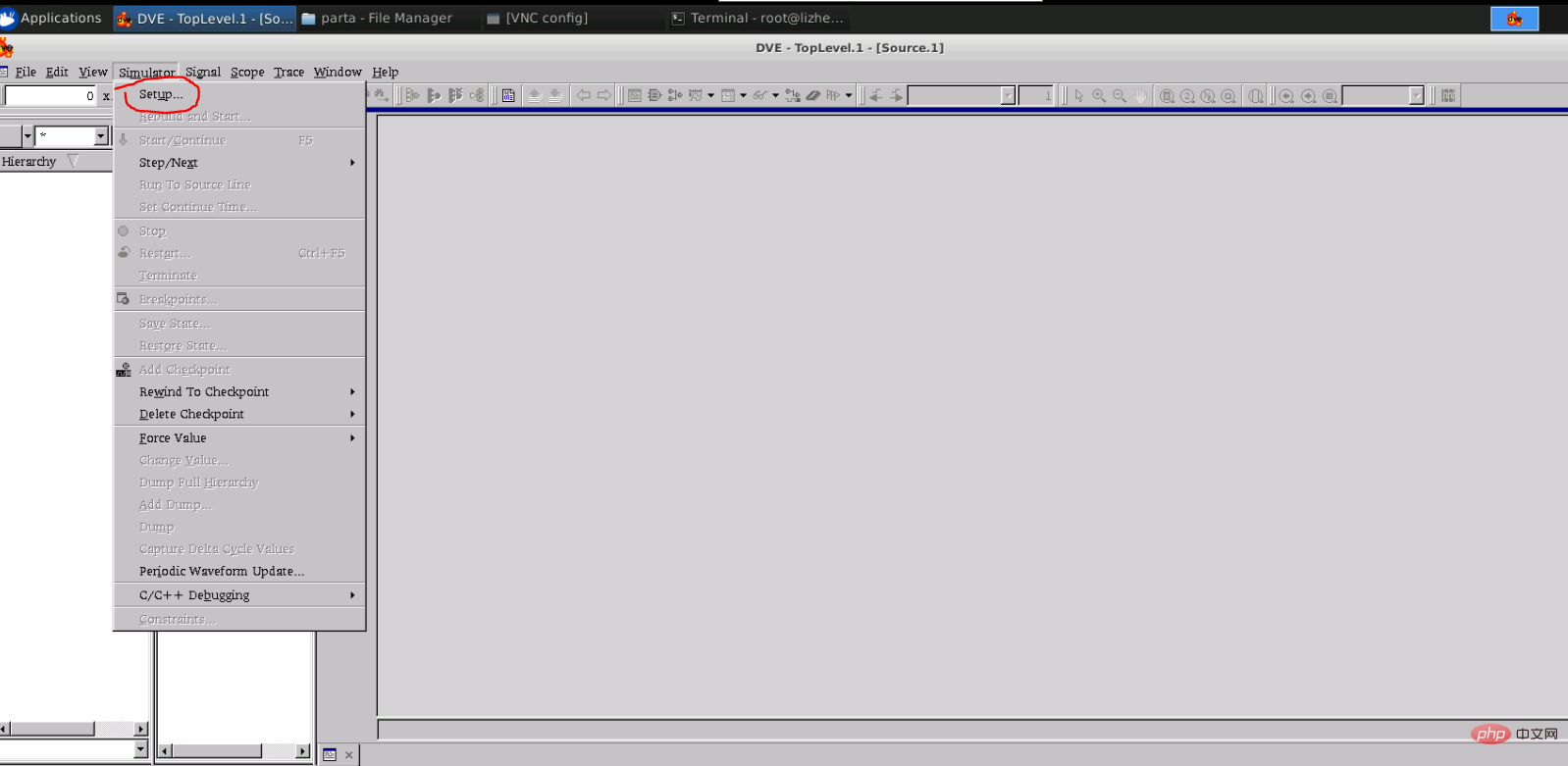

(3)如果以./simv執行會直接看到波形文件,如果使用dve & 需要自行加入simv文件來查看波形,選取simulator->Setup,加入產生的simv檔。

在下方run all,如果沒有給時間刻度這裡會報錯。沒有報錯,則表示我們的功能是完全正確無誤的。右鍵加入波形文件,按f鍵顯示波形。

(4)如下的四個按鍵作用

第一個: 追蹤誰來驅動該訊號ctrl d

第二個: 追蹤訊號的值轉換ctrl shift d

第三個:追蹤未知態

第四個: 追蹤用來驅動誰

vcs的腳本寫法可以幫助快遞進行模擬得到波形檔。

其中.PHONY可以指定對應哪些關鍵字進行make操作。

.PHONY:vcs sim dve clean

OUTPUT = adder

VCS = vcs -sverilog +v2k -timescale=1ns/1ns \

-debug_all \

-o ${OUTPUT} \

-l compile.log \SIM = ./${OUTPUT} -l run.log

vcs: ${VCS} -f verilog_file.f

sim: ${SIM}dve:

dve -vpd vcdplus.vpd & clean: rm -rf *.log csrc simv* *.key *.vpd DVEfiles coverage *.vdb這樣 make vcs執行vcs語句,make sim執行simv語句,make dve開啟波形文件,make clean清除一些冗餘檔案。

其中,verilog_file.f是檔案的列表,可以採用下面語句生成,這樣將所有以v結尾的檔案名稱寫到目標檔案中。

find -name ".*v" > file.list

以上是linux vcs是什麼的詳細內容。更多資訊請關注PHP中文網其他相關文章!