DDR5 MRDIMM 和 LPDDR6 CAMM 内存规范蓄势待发,JEDEC 公布关键技术细节

本站 7 月 23 日消息,微电子标准制定方 JEDEC 固态技术协会当地时间 22 日宣布,DDR5 MRDIMM 和 LPDDR6 CAMM 内存技术规范即将正式推出,并介绍了这两项内存的关键细节。

DDR5 MRDIMM 中的“MR”即 Multiplexed Rank(多路复用列),这意味着该内存支持两个或以上的 Rank(列),并可在单个通道上组合和传输多个数据信号,无需额外的物理连接就能有效提升带宽。

JEDEC 规划了多代 DDR5 MRDIMM内存,目标最终将其带宽提升至 12.8Gbps,较 DDR5 RDIMM 内存目前的 6.4Gbps 翻倍。

在 JEDEC 的设想中,DDR5 MRDIMM 将利用与现有 DDR5 DIMM 相同的引脚、SPD、PMIC 等设计,与 RDIMM 平台兼容,并利用现有的 LRDIMM 生态系统进行设计与测试。

此外 JEDEC 还规划了 Tall MRDIMM 外形尺寸。正如其名,这一设计将采用更高的外形尺寸,使其支持的 DRAM 封装数量翻倍,可进一步提升内存容量。

而在 LPDDR6 CAMM 方面,JEDEC 表示预计将实现 14.4GT/s 以上的最大速度,同时将提到 24bit 位宽子通道、48bit 位宽通道并支持“连接器阵列”(本站注:原文为 connector array)。

以上是DDR5 MRDIMM 和 LPDDR6 CAMM 内存规范蓄势待发,JEDEC 公布关键技术细节的详细内容。更多信息请关注PHP中文网其他相关文章!

热AI工具

Undresser.AI Undress

人工智能驱动的应用程序,用于创建逼真的裸体照片

AI Clothes Remover

用于从照片中去除衣服的在线人工智能工具。

Undress AI Tool

免费脱衣服图片

Clothoff.io

AI脱衣机

AI Hentai Generator

免费生成ai无尽的。

热门文章

热工具

记事本++7.3.1

好用且免费的代码编辑器

SublimeText3汉化版

中文版,非常好用

禅工作室 13.0.1

功能强大的PHP集成开发环境

Dreamweaver CS6

视觉化网页开发工具

SublimeText3 Mac版

神级代码编辑软件(SublimeText3)

热门话题

打印机内存不足,无法打印页面Excel或PowerPoint错误

Feb 19, 2024 pm 05:45 PM

打印机内存不足,无法打印页面Excel或PowerPoint错误

Feb 19, 2024 pm 05:45 PM

如果在打印Excel工作表或PowerPoint演示文稿时遇到打印机内存不足的问题,这篇文章可能对您有所帮助。您可能收到类似的错误消息,指出打印机内存不足,无法打印页面。不过,您可以遵循一些建议来解决这个问题。为什么打印时打印机内存不可用?打印机内存不足可能导致内存不可用错误。有时是由于打印机驱动程序设置过低,也可能是其他原因。大文件大小打印机驱动程序过时或损坏来自已安装的加载项的中断打印机设置配置错误发生此问题也可能是因为MicrosoftWindows打印机驱动程序上的内存设置较低。修复打印

大内存优化,电脑升级16g/32g内存速度没什么变化怎么办?

Jun 18, 2024 pm 06:51 PM

大内存优化,电脑升级16g/32g内存速度没什么变化怎么办?

Jun 18, 2024 pm 06:51 PM

对于机械硬盘、或SATA固态硬盘,软件运行速度的提升会有感觉,如果是NVME硬盘,可能感觉不到。一,注册表导入桌面新建一个文本文档,复制粘贴如下内容,另存为1.reg,然后右键合并,并重启电脑。WindowsRegistryEditorVersion5.00[HKEY_LOCAL_MACHINE\SYSTEM\CurrentControlSet\Control\SessionManager\MemoryManagement]"DisablePagingExecutive"=d

小米14Pro如何查看内存占用?

Mar 18, 2024 pm 02:19 PM

小米14Pro如何查看内存占用?

Mar 18, 2024 pm 02:19 PM

最近,小米发布了一款功能强大的高端智能手机小米14Pro,它不仅外观设计时尚,而且拥有内在和外在的黑科技。该手机拥有顶级的性能和出色的多任务处理能力,让用户能够畅享快速而流畅的手机使用体验。但是性能也是会收到内存的影响的,很多用户们想要知道小米14Pro如何查看内存占用,赶快来看看吧。小米14Pro如何查看内存占用?小米14Pro查看内存占用方法介绍打开小米14Pro手机【设置】中的【应用管理】按钮。查看已安装的所有应用列表,浏览列表并找到你想查看的应用,点击它进入应用详细页面。在应用详细页面中

![Windows输入遇到挂起或内存使用率高的问题[修复]](https://img.php.cn/upload/article/000/887/227/170835409686241.jpg?x-oss-process=image/resize,m_fill,h_207,w_330) Windows输入遇到挂起或内存使用率高的问题[修复]

Feb 19, 2024 pm 10:48 PM

Windows输入遇到挂起或内存使用率高的问题[修复]

Feb 19, 2024 pm 10:48 PM

Windows的输入体验是一个关键的系统服务,负责处理来自各种人机接口设备的用户输入。它在系统启动时自动启动,在后台运行。然而,有时候这个服务可能会出现自动挂起或占用过多内存的情况,导致系统性能下降。因此,及时监控和管理这个进程是至关重要的,以确保系统的效率和稳定性。在这篇文章中,我们将分享如何解决Windows输入体验被挂起或导致内存使用率高的问题。Windows输入体验服务没有用户界面,但它与处理与输入设备相关的基本系统任务和功能有密切关联。它的作用是帮助Windows系统理解用户输入的每一

电脑8g和16g内存区别大吗?(电脑内存选8g还是16g)

Mar 13, 2024 pm 06:10 PM

电脑8g和16g内存区别大吗?(电脑内存选8g还是16g)

Mar 13, 2024 pm 06:10 PM

新手用户在购买电脑时,会好奇电脑内存8g和16g有什么区别?应该选择8g还是16g呢?针对这个问题,今天小编就来跟大家详细说明一下。 电脑内存8g和16g的区别大吗? 1、在一般家庭或者是普通工作使用,8G运行内存可以满足,因此在使用过程中8g和16g区别不大。 2、游戏爱好者使用时候,目前大型游戏基本上是6g起步,8g是最低标准。目前在屏幕是2k的情况下,更高分辨率并不会带来更高的帧数表现,因此对8g和16g也无较大差异。 3、对于音频、视频剪辑使用者来说,8g和16g会出现明显区

消息称三星电子、SK 海力士堆叠式移动内存 2026 年后商业化

Sep 03, 2024 pm 02:15 PM

消息称三星电子、SK 海力士堆叠式移动内存 2026 年后商业化

Sep 03, 2024 pm 02:15 PM

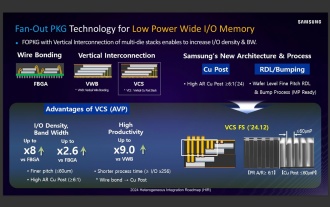

本站9月3日消息,韩媒etnews当地时间昨日报道称,三星电子和SK海力士的“类HBM式”堆叠结构移动内存产品将在2026年后实现商业化。消息人士表示这两大韩国内存巨头将堆叠式移动内存视为未来重要收入来源,计划将“类HBM内存”扩展到智能手机、平板电脑和笔记本电脑中,为端侧AI提供动力。综合本站此前报道,三星电子的此类产品叫做LPWideI/O内存,SK海力士则将这方面技术称为VFO。两家企业使用了大致相同的技术路线,即将扇出封装和垂直通道结合在一起。三星电子的LPWideI/O内存位宽达512

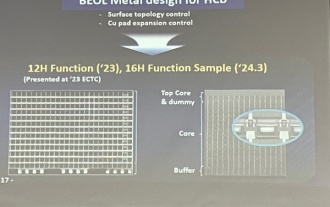

三星宣布完成 16 层混合键合堆叠工艺技术验证,有望在 HBM4 内存大面积应用

Apr 07, 2024 pm 09:19 PM

三星宣布完成 16 层混合键合堆叠工艺技术验证,有望在 HBM4 内存大面积应用

Apr 07, 2024 pm 09:19 PM

报道称,三星电子的高管DaeWooKim表示,在2024年韩国微电子和封装学会年会上,三星电子将完成采用16层混合键合HBM内存技术的验证。据悉,这项技术已通过技术验证。报道还称,此次技术验证将为未来若干年内的内存市场发展奠定基础。DaeWooKim表示,三星电子成功制造了基于混合键合技术的16层堆叠HBM3内存,该内存样品工作正常,未来16层堆叠混合键合技术将用于HBM4内存量产。▲图源TheElec,下同相较现有键合工艺,混合键合无需在DRAM内存层间添加凸块,而是将上下两层直接铜对铜连接,

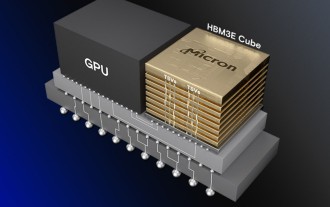

美光:HBM 内存消耗 3 倍晶圆量,明年产能基本预定完毕

Mar 22, 2024 pm 08:16 PM

美光:HBM 内存消耗 3 倍晶圆量,明年产能基本预定完毕

Mar 22, 2024 pm 08:16 PM

本站3月21日消息,美光在发布季度财报后举行了电话会议。在该会议上美光CEO桑杰・梅赫罗特拉(SanjayMehrotra)表示,相对于传统内存,HBM对晶圆量的消耗明显更高。美光表示,在同一节点生产同等容量的情况下,目前最先进的HBM3E内存对晶圆量的消耗是标准DDR5的三倍,并且预计随着性能的提升和封装复杂度的加剧,在未来的HBM4上这一比值将进一步提升。参考本站以往报道,这一高比值有相当一部分原因在HBM的低良率上。HBM内存采用多层DRAM内存TSV连接堆叠而成,一层出现问题就意味着整个