UCIe 2.0:通过 3D 封装和可管理性推进开放式小芯片生态系统

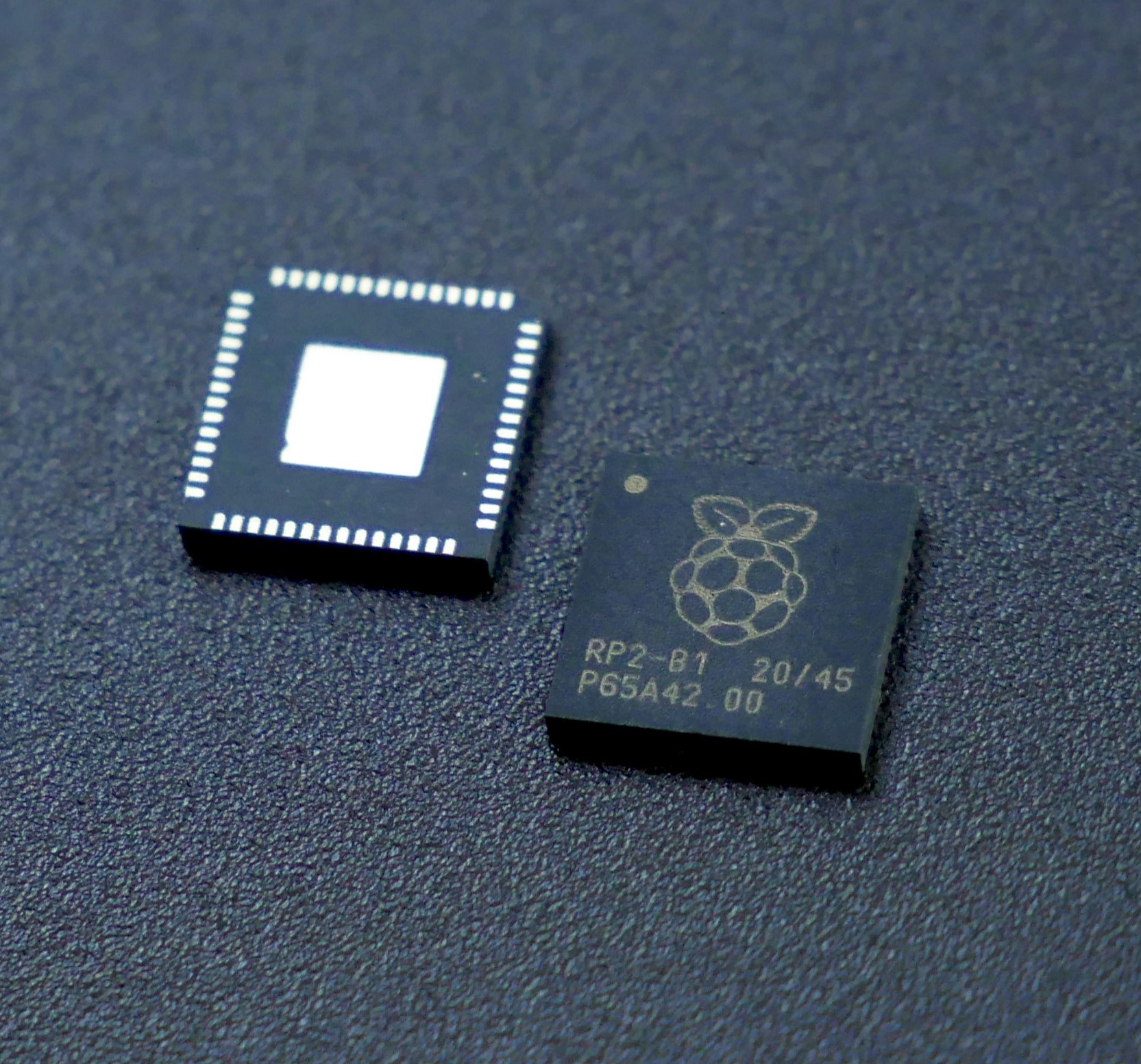

通用 Chiplet Interconnect Express (UCIe) 联盟宣布发布 UCIe 2.0 规范,进一步推进开放式 Chiplet 生态系统。

最新规范引入了几项关键增强功能。首先,它增加了对标准化系统架构的支持,以实现整个系统级封装 (SiP) 生命周期中跨多个芯片组的可管理性、可测试性和调试 (DFx)。其中包括可选的 UCIe DFx 架构 (UDA),该架构在每个小芯片内集成了供应商无关的管理结构,用于测试、遥测和调试功能。

此外,UCIe 2.0 还支持混合键合 3D 封装。新的 UCIe-3D 标准支持小至 1 微米至大 25 微米的凸块间距,与 2D 和 2.5D 架构相比,可实现更高的带宽密度和更高的功率效率。三星电子总裁兼公司副总裁 Cheolmin Park 表示:“UCIe 联盟正在支持各种芯片组,以满足快速变化的半导体行业的需求。”

UCIe 2.0 规范以之前的迭代为基础,开发了全面的解决方案堆栈并鼓励芯片组解决方案之间的互操作性。

该规范还包括优化的封装设计,以促进互操作性和合规性测试,使供应商能够根据已知的参考实现来验证其基于 UCIe 的设备所支持的功能。

值得注意的是,UCIe 2.0 规范仍然完全向后兼容 UCIe 1.1 和 1.0,确保现有基于 Chiplet 的设计平稳过渡。

以上是UCIe 2.0:通过 3D 封装和可管理性推进开放式小芯片生态系统的详细内容。更多信息请关注PHP中文网其他相关文章!

热AI工具

Undresser.AI Undress

人工智能驱动的应用程序,用于创建逼真的裸体照片

AI Clothes Remover

用于从照片中去除衣服的在线人工智能工具。

Undress AI Tool

免费脱衣服图片

Clothoff.io

AI脱衣机

Video Face Swap

使用我们完全免费的人工智能换脸工具轻松在任何视频中换脸!

热门文章

热工具

记事本++7.3.1

好用且免费的代码编辑器

SublimeText3汉化版

中文版,非常好用

禅工作室 13.0.1

功能强大的PHP集成开发环境

Dreamweaver CS6

视觉化网页开发工具

SublimeText3 Mac版

神级代码编辑软件(SublimeText3)

华为Watch GT 5智能手表获得新功能更新

Oct 03, 2024 am 06:25 AM

华为Watch GT 5智能手表获得新功能更新

Oct 03, 2024 am 06:25 AM

华为正在全球推出Watch GT 5和Watch GT 5 Pro智能手表的软件版本5.0.0.100(C00M01)。这两款智能手表最近在欧洲推出,标准型号是该公司最便宜的型号。这和谐

铁拳桑德斯上校的梦想被肯德基炸了

Oct 02, 2024 am 06:07 AM

铁拳桑德斯上校的梦想被肯德基炸了

Oct 02, 2024 am 06:07 AM

《铁拳》系列总监原田胜宏曾认真尝试过将桑德斯上校带入这款标志性格斗游戏中。在接受 TheGamer 采访时,原田透露,他向日本肯德基提出了这个想法,希望将这位快餐传奇人物纳入其中。

Cybertruck FSD 评论称赞快速车道切换和全屏可视化

Oct 01, 2024 am 06:16 AM

Cybertruck FSD 评论称赞快速车道切换和全屏可视化

Oct 01, 2024 am 06:16 AM

特斯拉正在推出最新的全自动驾驶(监督)版本 12.5.5,并最终带来了承诺的 Cybertruck FSD 选项,距离皮卡上市十个月后,该功能包含在基础系列的装饰价格中。 F

Garmin 通过新的更新发布了针对多款智能手表的冒险赛车活动改进

Oct 01, 2024 am 06:40 AM

Garmin 通过新的更新发布了针对多款智能手表的冒险赛车活动改进

Oct 01, 2024 am 06:40 AM

Garmin 将于本月底为其最新的高端智能手表提供一组新的稳定更新。回顾一下,该公司发布了系统软件 11.64,以解决 Enduro 3、Fenix E 和 Fenix 8 的高电池消耗问题(亚马逊售价 1,099.99 美元)。

搭载 HyperOS 的新款小米米家石墨烯油汀到货

Oct 02, 2024 pm 09:02 PM

搭载 HyperOS 的新款小米米家石墨烯油汀到货

Oct 02, 2024 pm 09:02 PM

小米即将在中国推出米家石墨烯油汀取暖器。该公司最近在其优品平台上成功举办了一次智能家居产品众筹活动。根据页面显示,该设备已经开始发货至

第一眼:即将推出的 Anker Zolo 4 端口 140W 带显示屏壁式充电器的拆箱视频泄露

Oct 01, 2024 am 06:32 AM

第一眼:即将推出的 Anker Zolo 4 端口 140W 带显示屏壁式充电器的拆箱视频泄露

Oct 01, 2024 am 06:32 AM

2024 年 9 月早些时候,Anker 的 Zolo 140W 充电器被泄露,这是该公司首款带显示屏的壁式充电器,这引起了轰动。现在,小李TV在YouTube上发布的新开箱视频让我们亲眼目睹了这款hi

三星 Galaxy Z Fold 特别版透露将于 10 月底登陆,但名称出现冲突

Oct 01, 2024 am 06:21 AM

三星 Galaxy Z Fold 特别版透露将于 10 月底登陆,但名称出现冲突

Oct 01, 2024 am 06:21 AM

三星期待已久的“特别版”可折叠手机的推出又迎来了另一个转折。最近几周,有关所谓 Galaxy Z Fold 特别版的传言相当安静。相反,焦点已转移到 Galaxy S25 系列,包括

Manjaro 24.1'Xahea”与 KDE Plasma 6.1.5、VirtualBox 7.1 等一起发布

Oct 02, 2024 am 06:06 AM

Manjaro 24.1'Xahea”与 KDE Plasma 6.1.5、VirtualBox 7.1 等一起发布

Oct 02, 2024 am 06:06 AM

Manjaro 已有十多年的历史,被认为是最用户友好的 Linux 发行版之一,适合初学者和高级用户,易于安装和使用。这个基于 Arch 的发行版主要在奥地利、德国和法国开发