为解决cpu与主存的速度匹配可采用什么

为解决cpu与主存的速度匹配可采用cache存储器。cache存储器是位于cpu和主存储器DRAM之间,规模较小,但速度很高的存储器,通常由静态存储器组成。静态存储器是位于cpu与内存间的一种容量较小但速度很高的存储器。

本教程操作环境:windows7系统、Dell G3电脑。

为解决CPU和主存的速度匹配问题,其实现可采用介于CPU和主存之间的Cache。

cache是什么

Cache存储器,电脑中为高速缓冲存储器,是位于CPU和主存储器DRAM(Dynamic Random Access Memory)之间,规模较小,但速度很高的存储器,通常由SRAM(Static Random Access Memory 静态存储器)组成。它是位于CPU与内存间的一种容量较小但速度很高的存储器。

CPU的速度远高于内存,当CPU直接从内存中存取数据时要等待一定时间周期,而Cache则可以保存CPU刚用过或循环使用的一部分数据,如果CPU需要再次使用该部分数据时可从Cache中直接调用,这样就避免了重复存取数据,减少了CPU的等待时间,因而提高了系统的效率。

cache的功能

Cache的功能是提高CPU数据输入输出的速率。Cache容量小但速度快,内存速度较低但容量大,通过优化调度算法,系统的性能会大大改善,仿佛其存储系统容量与内存相当而访问速度近似Cache。

CPU的速度远高于内存,当CPU直接从内存中存取数据时要等待一定时间周期,而Cache则可以保存CPU刚用过或循环使用的一部分数据,如果CPU需要再次使用该部分数据时可从Cache中直接调用,这样就避免了重复存取数据,减少了CPU的等待时间,因而提高了系统的效率。Cache又分为L1Cache(一级缓存)和L2Cache(二级缓存),L1Cache主要是集成在CPU内部,而L2Cache集成在主板上或是CPU上。

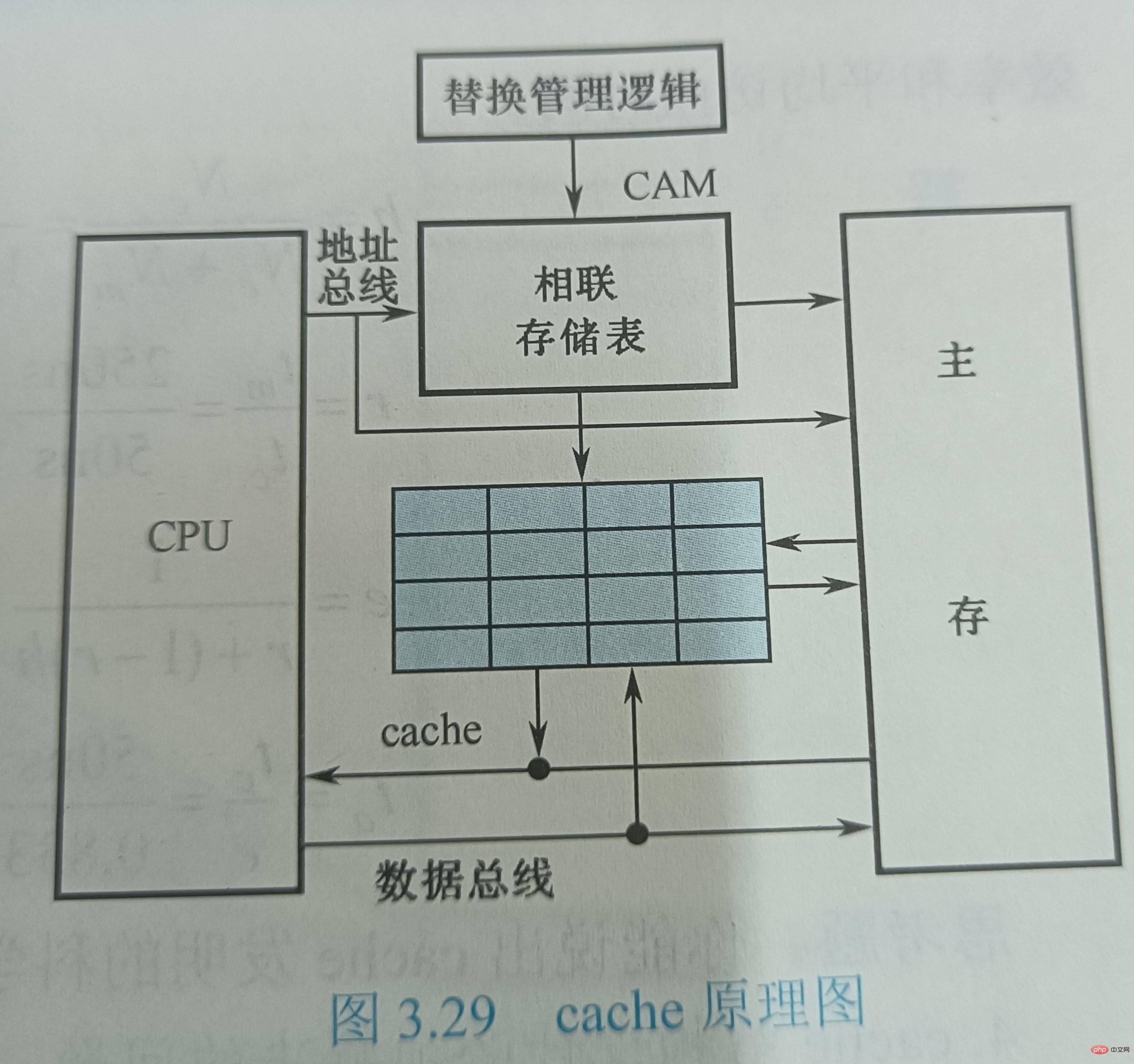

cache的基本原理

cache除包含SRAM外,还要有控制逻辑。若cache在CPU芯片外,它的控制逻辑一般与主存控制逻辑合成在一起,称为主存/chace控制器;若cache在CPU内,则由CPU提供它的控制逻辑。

CPU与cache之间的数据交换是以字为单位,而cache与主存之间的数据交换是以块为单位。一个块由若干字组成,是定长的。当CPU读取内存中一个字时,便发出此字的内存地址到cache和主存。此时cache控制逻辑依据地址判断此字当前是否在cache中:若是,则cache命中,此字立即传送给CPU;若非,则cache缺失(未命中),用主存读周期把此字从主存读出送到CPU,与此同时,把含有这个字的整个数据块从主存读出送到cache中。

图3.29示出了cache的原理图。假设cache读出时间为50ns,主存读出时间为250ns。存储系统是模块化的,主存中每个8K模块和容量16字的cache相联系。cache分为4行,每行4个字(W)。分配给cache的地址存放在一个相联存储器CAM中,它是按内容寻址的存储器。当CPU执行访存指令时,就把所要访问的字的地址送到CAM;如果W不在cache中,则将W从主存传送到CPU。与此同时,把包含W的由前后相继的4个字所组成的一行数据送入cache,替换原来cache中的一行数据。在这里,由始终管理cache使用情况的硬件逻辑电路来实现替换算法。

cache结构设计必须解决的问题

从cache的基本工作原理可以看出, cache的设计需要遵循两个原则:一是希望cache的命中率尽可能高,实际应接近于1;二是希望cache对CPU而言是透明的,即不论是否有cache, CPU访存的方法都是一样的,软件不需增加任何指令就可以访问cache。解决了命中率和透明性问题,就CPU访存的角度而言,内存将具有主存的容量和接近cache的速度。为此,必须增加一定的硬件电路完成控制功能,即cache控制器。

在设计cache结构时,必须解决几个问题:①主存的内容调入cache时如何存放?②访存时如何找到cache中的信息?③当cache空间不足时如何替换cache中已有的内容?④需要写操作时如何改写cache的内容?

其中,前两个问题是相互关联的,即如何将主存信息定位在cache中,如何将主存地址变换为cache地址。与主存容量相比, cache的容量很小,它保存的内容只是主存内容的一个子集,且cache与主存的数据交换是以块为单位。为了把主存块放到cache中,必须应用某种方法把主存地址定位到cache中,称为地址映射。“映射”一词的物理含义是确定位置的对应关系,并用硬件来实现。这样当CPU访问存储器时,它所给出的一个字的内存地址会自动变换成cache的地址,即cache地址变换。

cache替换问题主要是选择和执行替换算法,以便在cache不命中时替换cache中的内容。最后一个问题涉及cache的写操作策略,重点是在更新时保持主存与cache的一致性。

(学习视频分享:编程视频)

以上是为解决cpu与主存的速度匹配可采用什么的详细内容。更多信息请关注PHP中文网其他相关文章!

热AI工具

Undresser.AI Undress

人工智能驱动的应用程序,用于创建逼真的裸体照片

AI Clothes Remover

用于从照片中去除衣服的在线人工智能工具。

Undress AI Tool

免费脱衣服图片

Clothoff.io

AI脱衣机

AI Hentai Generator

免费生成ai无尽的。

热门文章

热工具

记事本++7.3.1

好用且免费的代码编辑器

SublimeText3汉化版

中文版,非常好用

禅工作室 13.0.1

功能强大的PHP集成开发环境

Dreamweaver CS6

视觉化网页开发工具

SublimeText3 Mac版

神级代码编辑软件(SublimeText3)

热门话题

在游戏时,CPU利用率应该是多少?

Feb 19, 2024 am 11:21 AM

在游戏时,CPU利用率应该是多少?

Feb 19, 2024 am 11:21 AM

游戏因消耗大量资源而导致电脑运行速度变慢是常见现象。了解游戏时CPU的使用率是至关重要的,这样可以避免过度负荷。因此,掌握适当的CPU使用率是保持游戏体验流畅的关键。在本文中,我们将探讨游戏运行时CPU应该达到的合适使用率。游戏时的CPU利用率CPU使用率是指衡量处理器工作负载的一个重要指标,取决于CPU的性能规格。功率更大的CPU通常具有更高的使用率。拥有更多核心和线程的CPU可以提高系统的整体性能。多线程支持有助于充分发挥CPU的潜力。在游戏中,CPU使用率取决于处理器的利用率,这可影响游戏

Win11如何设置CPU性能全开

Feb 19, 2024 pm 07:42 PM

Win11如何设置CPU性能全开

Feb 19, 2024 pm 07:42 PM

很多用户在使用Win11系统时发现电脑运行不够流畅,想要提升CPU性能,但不清楚如何操作。下面将详细介绍如何在Win11系统中设置CPU性能至最高,让您的电脑更加高效。设置方法:1、右击桌面上的”此电脑”,选择选项列表中的”属性”。2、进入到新的界面后,点击”相关链接”中的”高级系统设置”。3、在打开的窗口中,点击上方中的”高级”选项卡,接着点击”性能”下方中的&

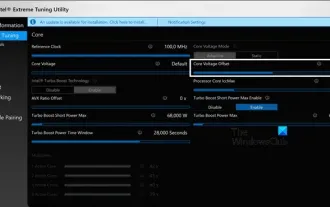

如何使用Intel XTU对CPU进行欠压和超频

Feb 19, 2024 am 11:06 AM

如何使用Intel XTU对CPU进行欠压和超频

Feb 19, 2024 am 11:06 AM

英特尔XTU是一款强大的应用程序,可让您轻松管理计算机的性能。您可以通过调整CPU电压来解决过热问题,或者通过超频来提升性能。在这篇文章中,我们将探讨如何利用英特尔XTU来优化计算机的性能,无论是调整电压还是进行超频。欠压和超频对CPU有什么作用?在我们继续学习如何对CPU进行欠压和超频之前,首先必须了解它们是什么。欠电压指的是逐渐降低CPU所需的电压。这一过程有助于减少热量排放,因为高电压会导致更高的温度。通过减少CPU的电压供应,可以有效地降低温度。如果笔记本在发热后开始减速,应及时解决问题

如何增加电脑CPU的时钟频率

Feb 20, 2024 am 09:54 AM

如何增加电脑CPU的时钟频率

Feb 20, 2024 am 09:54 AM

电脑CPU如何超频随着科技的不断进步,人们对于电脑性能的需求也越来越高。而一种有效的提升电脑性能的方法就是通过超频(overclocking)来增加CPU的工作频率。超频可以使CPU更快地处理数据,从而提供更高的计算能力。那么,电脑CPU如何超频呢?下面将为大家介绍超频的基本原理和具体操作方法。首先,让我们了解一下超频的原理。CPU的工作频率是由主板上的晶振

WIN10服务主机太占cpu的处理操作过程

Mar 27, 2024 pm 02:41 PM

WIN10服务主机太占cpu的处理操作过程

Mar 27, 2024 pm 02:41 PM

1、首先我们右击任务栏空白处,选择【任务管理器】选项,或者右击开始徽标,然后再选择【任务管理器】选项。2、在打开的任务管理器界面,我们点击最右端的【服务】选项卡。3、在打开的【服务】选项卡,点击下方的【打开服务】选项。4、在打开的【服务】窗口,右击【InternetConnectionSharing(ICS)】服务,然后选择【属性】选项。5、在打开的属性窗口,将【打开方式】修改为【禁用】,点击【应用】后点击【确定】。6、点击开始徽标,然后点击关机按钮,选择【重启】,完成电脑重启就行了。

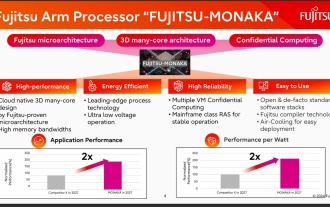

144 核心,3D 堆叠 SRAM:富士通详细介绍下一代数据中心处理器 MONAKA

Jul 29, 2024 am 11:40 AM

144 核心,3D 堆叠 SRAM:富士通详细介绍下一代数据中心处理器 MONAKA

Jul 29, 2024 am 11:40 AM

本站7月28日消息,据外媒TechRader报道,富士通详细介绍了计划于2027年出货的FUJITSU-MONAKA(以下简称MONAKA)处理器。MONAKACPU基于“云原生3D众核”架构,采用Arm指令集,面向数据中心、边缘与电信领域,适用于AI计算,能实现大型机级别的RAS1。富士通表示,MONAKA将在能效和性能方面实现飞跃:得益于超低电压(ULV)工艺等技术,该CPU可实现2027年竞品2倍的能效,冷却无需水冷;此外该处理器的应用性能也可达对手2倍。在指令方面,MONAKA配备的矢量

泄漏揭示了英特尔 Arrow Lake-U、-H、-HX 和 -S 的关键规格

Jun 15, 2024 pm 09:49 PM

泄漏揭示了英特尔 Arrow Lake-U、-H、-HX 和 -S 的关键规格

Jun 15, 2024 pm 09:49 PM

英特尔ArrowLake预计将基于与LunarLake相同的处理器架构,这意味着英特尔全新的LionCove性能核心将与经济的Skymont效率核心相结合。而LunarLake仅作为ava推出

AM4 拒绝死亡,消息称 AMD 将推出 Ryzen 9 5900XT /7 5800XT:主频最高 4.8GHz

Jun 05, 2024 pm 09:43 PM

AM4 拒绝死亡,消息称 AMD 将推出 Ryzen 9 5900XT /7 5800XT:主频最高 4.8GHz

Jun 05, 2024 pm 09:43 PM

本站6月1日消息,消息源@CodeCommando今天发布推文,分享了AMD即将在Computex2024活动中的部分演示文档截图,推文内容为“AM4永不消亡”,配图展示了两款新的Ryzen5000XT系列处理器。根据截图内容显示以下两款产品:Ryzen95900XTRyzen95900XT定位相对高端,这是一款全新的16核AM4处理器,其时钟速度略低于AMD的Ryzen95950X。Ryzen75800XT它是AMD现有Ryzen75800X处理器的更快变体,这两款处理器的主频最高可达4.8G