组成cpu的元器件包括哪些

组成cpu的元器件包括“运算器”和“控制器”。cpu(中央处理器)主要包括两个部分:1、运算器,是指计算机中进行各种算术和逻辑运算操作的部件, 其中算术逻辑单元是中央处理核心的部分;2、控制器,是指按照预定顺序改变主电路或控制电路的接线和改变电路中电阻值来控制电动机的启动、调速、制动与反向的主令装置。

本教程操作环境:windows7系统、Dell G3电脑。

组成cpu的元器件包括“运算器”和“控制器”。

中央处理器(central processing unit,简称CPU)作为计算机系统的运算和控制核心,是信息处理、程序运行的最终执行单元。CPU自产生以来,在逻辑结构、运行效率以及功能外延上取得了巨大发展。

中央处理器(CPU),是电子计算机的主要设备之一,电脑中的核心配件。其功能主要是解释计算机指令以及处理计算机软件中的数据。CPU是计算机中负责读取指令,对指令译码并执行指令的核心部件。中央处理器主要包括两个部分,即控制器、运算器,其对提高计算机的整体功能起着重要作用,能够实现寄存控制、逻辑运算、信号收发等多项功能的扩散,为提升计算机的性能奠定良好基础。

运算器

运算器是指计算机中进行各种算术和逻辑运算操作的部件, 其中算术逻辑单元是中央处理核心的部分。

(1)算术逻辑单元(ALU)。算术逻辑单元是指能实现多组 算术运算与逻辑运算的组合逻辑电路,其是中央处理中的重要组成部分。算术逻辑单元的运算主要是进行二位元算术运算,如加法、减法、乘法。在运算过程中,算术逻辑单元主要是以计算机指令集中执行算术与逻辑操作,通常来说,ALU能够发挥直接读入读出的作用,具体体现在处理器控制器、内存及输入输出设备等方面,输入输出是建立在总线的基础上实施。输入指令包含一 个指令字,其中包括操作码、格式码等。

(2)中间寄存器(IR)。其长度为 128 位,其通过操作数来决定实际长度。IR 在“进栈并取数”指令中发挥重要作用,在执行该指令过程中,将ACC的内容发送于IR,之后将操作数取到ACC,后将IR内容进栈。

(3)运算累加器(ACC)。当前的寄存器一般都是单累加器,其长度为128位。对于ACC来说,可以将它看成可变长的累加器。在叙述指令过程中,ACC长度的表示一般都是将ACS的值作为依据,而ACS长度与 ACC 长度有着直接联系,ACS长度的加倍或减半也可以看作ACC长度加倍或减半。

(4)描述字寄存器(DR)。其主要应用于存放与修改描述字中。DR的长度为64位,为了简化数据结构处理,使用描述字发挥重要作用。 [2]

(5)B寄存器。其在指令的修改中发挥重要作用,B 寄存器长度为32位,在修改地址过程中能保存地址修改量,主存地址只能用描述字进行修改。指向数组中的第一个元素就是描述字, 因此,访问数组中的其它元素应当需要用修改量。对于数组成来说,其是由大小一样的数据或者大小相同的元素组成的,且连续存储,常见的访问方式为向量描述字,因为向量描述字中的地址为字节地址,所以,在进行换算过程中,首先应当进行基本地址 的相加。对于换算工作来说,主要是由硬件自动实现,在这个过程中尤其要注意对齐,以免越出数组界限。

控制器

控制器是计算机的神经中枢,指挥全机中各个部件自动协调工作。在控制器的控制下,计算机能够自动按照程序设定的步骤进行一系列操作,以完成特定任务。

控制器是指按照预定顺序改变主电路或控制电路的接线和改变电路中电阻值来控制电动机的启动、调速、制动与反向的主令装置。控制器由程序状态寄存器PSR,系统状态寄存器SSR, 程序计数器PC,指令寄存器等组成,其作为“决策机构”,主要任务就是发布命令,发挥着整个计算机系统操作的协调与指挥作用。 控制的分类主要包括两种,分别为组合逻辑控制器、微程序控制器,两个部分都有各自的优点与不足。其中组合逻辑控制器结构相对较复杂,但优点是速度较快;微程序控制器设计的结构简单,但在修改一条机器指令功能中,需对微程序的全部重编。

控制器内部的主要部件如下:

①指令寄存器:存放由存储器取得的指令。

②译码器:将指令中的操作码翻译成控制信号。

③时序节拍发生器:产生时序脉冲节拍信号,使计算机有节奏、有次序地工作。

④操作控制部件:将控制信号组合起来,控制各个部件完成相应的操作。

⑤指令计数器:计算并指出下一条指令的地址。

扩展知识:CPU的工作原理

冯诺依曼体系结构是现代计算机的基础。在该体系结构下,程序和数据统一存储,指令和数据需要从同一存储空间存取,经由同一总线传输,无法重叠执行。根据冯诺依曼体系,CPU的工作分为以下 5 个阶段:取指令阶段、指令译码阶段、执行指令阶段、访存取数和结果写回。

取指令(IF,instruction fetch),即将一条指令从主存储器中取到指令寄存器的过程。程序计数器中的数值,用来指示当前指令在主存中的位置。当 一条指令被取出后,程序计数器(PC)中的数值将根据指令字长度自动递增。

指令译码阶段(ID,instruction decode),取出指令后,指令译码器按照预定的指令格式,对取回的指令进行拆分和解释,识别区分出不同的指令类 别以及各种获取操作数的方法。现代CISC处理器会将拆分已提高并行率和效率。

执行指令阶段(EX,execute),具体实现指令的功能。CPU的不同部分被连接起来,以执行所需的操作。

访存取数阶段(MEM,memory),根据指令需要访问主存、读取操作数,CPU得到操作数在主存中的地址,并从主存中读取该操作数用于运算。部分指令不需要访问主存,则可以跳过该阶段。

结果写回阶段(WB,write back),作为最后一个阶段,结果写回阶段把执行指令阶段的运行结果数据“写回”到某种存储形式。结果数据一般会被写到CPU的内部寄存器中,以便被后续的指令快速地存取;许多指令还会改变程序状态字寄存器中标志位的状态,这些标志位标识着不同的操作结果,可被用来影响程序的动作。

在指令执行完毕、结果数据写回之后,若无意外事件(如结果溢出等)发生,计算机就从程序计数器中取得下一条指令地址,开始新一轮的循环,下一个指令周期将顺序取出下一条指令。 许多复杂的CPU可以一次提取多个指令、解码,并且同时执行。

更多相关知识,请访问常见问题栏目!

以上是组成cpu的元器件包括哪些的详细内容。更多信息请关注PHP中文网其他相关文章!

热AI工具

Undresser.AI Undress

人工智能驱动的应用程序,用于创建逼真的裸体照片

AI Clothes Remover

用于从照片中去除衣服的在线人工智能工具。

Undress AI Tool

免费脱衣服图片

Clothoff.io

AI脱衣机

Video Face Swap

使用我们完全免费的人工智能换脸工具轻松在任何视频中换脸!

热门文章

热工具

记事本++7.3.1

好用且免费的代码编辑器

SublimeText3汉化版

中文版,非常好用

禅工作室 13.0.1

功能强大的PHP集成开发环境

Dreamweaver CS6

视觉化网页开发工具

SublimeText3 Mac版

神级代码编辑软件(SublimeText3)

在游戏时,CPU利用率应该是多少?

Feb 19, 2024 am 11:21 AM

在游戏时,CPU利用率应该是多少?

Feb 19, 2024 am 11:21 AM

游戏因消耗大量资源而导致电脑运行速度变慢是常见现象。了解游戏时CPU的使用率是至关重要的,这样可以避免过度负荷。因此,掌握适当的CPU使用率是保持游戏体验流畅的关键。在本文中,我们将探讨游戏运行时CPU应该达到的合适使用率。游戏时的CPU利用率CPU使用率是指衡量处理器工作负载的一个重要指标,取决于CPU的性能规格。功率更大的CPU通常具有更高的使用率。拥有更多核心和线程的CPU可以提高系统的整体性能。多线程支持有助于充分发挥CPU的潜力。在游戏中,CPU使用率取决于处理器的利用率,这可影响游戏

Win11如何设置CPU性能全开

Feb 19, 2024 pm 07:42 PM

Win11如何设置CPU性能全开

Feb 19, 2024 pm 07:42 PM

很多用户在使用Win11系统时发现电脑运行不够流畅,想要提升CPU性能,但不清楚如何操作。下面将详细介绍如何在Win11系统中设置CPU性能至最高,让您的电脑更加高效。设置方法:1、右击桌面上的”此电脑”,选择选项列表中的”属性”。2、进入到新的界面后,点击”相关链接”中的”高级系统设置”。3、在打开的窗口中,点击上方中的”高级”选项卡,接着点击”性能”下方中的&

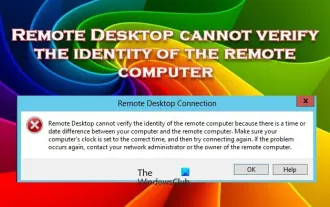

远程桌面无法验证远程计算机的身份

Feb 29, 2024 pm 12:30 PM

远程桌面无法验证远程计算机的身份

Feb 29, 2024 pm 12:30 PM

Windows远程桌面服务允许用户远程访问计算机,对于需要远程工作的人来说非常便利。然而,当用户无法连接到远程计算机或远程桌面无法验证计算机身份时,会遇到问题。这可能是由网络连接问题或证书验证失败引起的。在这种情况下,用户可能需要检查网络连接、确保远程计算机是在线的,并尝试重新连接。另外,确保远程计算机的身份验证选项已正确配置也是解决问题的关键。通过仔细检查和调整设置,通常可以解决Windows远程桌面服务中出现的这类问题。由于存在时间或日期差异,远程桌面无法验证远程计算机的身份。请确保您的计算

2024 CSRankings全美计算机科学排名发布!CMU霸榜,MIT跌出前5

Mar 25, 2024 pm 06:01 PM

2024 CSRankings全美计算机科学排名发布!CMU霸榜,MIT跌出前5

Mar 25, 2024 pm 06:01 PM

2024CSRankings全美计算机科学专业排名,刚刚发布了!今年,全美全美CS最佳大学排名中,卡耐基梅隆大学(CMU)在全美和CS领域均名列前茅,而伊利诺伊大学香槟分校(UIUC)连续六年稳定地位于第二。佐治亚理工学院则排名第三。然后,斯坦福大学、圣迭戈加利福尼亚大学、密歇根大学、华盛顿大学并列世界第四。值得注意的是,MIT排名下跌,跌出前五。CSRankings是由麻省州立大学阿姆赫斯特分校计算机与信息科学学院教授EmeryBerger发起的全球院校计算机科学领域排名项目。该排名基于客观的

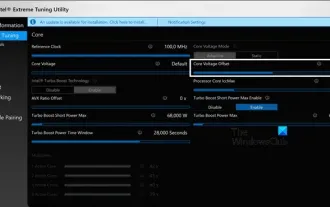

如何使用Intel XTU对CPU进行欠压和超频

Feb 19, 2024 am 11:06 AM

如何使用Intel XTU对CPU进行欠压和超频

Feb 19, 2024 am 11:06 AM

英特尔XTU是一款强大的应用程序,可让您轻松管理计算机的性能。您可以通过调整CPU电压来解决过热问题,或者通过超频来提升性能。在这篇文章中,我们将探讨如何利用英特尔XTU来优化计算机的性能,无论是调整电压还是进行超频。欠压和超频对CPU有什么作用?在我们继续学习如何对CPU进行欠压和超频之前,首先必须了解它们是什么。欠电压指的是逐渐降低CPU所需的电压。这一过程有助于减少热量排放,因为高电压会导致更高的温度。通过减少CPU的电压供应,可以有效地降低温度。如果笔记本在发热后开始减速,应及时解决问题

如何增加电脑CPU的时钟频率

Feb 20, 2024 am 09:54 AM

如何增加电脑CPU的时钟频率

Feb 20, 2024 am 09:54 AM

电脑CPU如何超频随着科技的不断进步,人们对于电脑性能的需求也越来越高。而一种有效的提升电脑性能的方法就是通过超频(overclocking)来增加CPU的工作频率。超频可以使CPU更快地处理数据,从而提供更高的计算能力。那么,电脑CPU如何超频呢?下面将为大家介绍超频的基本原理和具体操作方法。首先,让我们了解一下超频的原理。CPU的工作频率是由主板上的晶振

WIN10服务主机太占cpu的处理操作过程

Mar 27, 2024 pm 02:41 PM

WIN10服务主机太占cpu的处理操作过程

Mar 27, 2024 pm 02:41 PM

1、首先我们右击任务栏空白处,选择【任务管理器】选项,或者右击开始徽标,然后再选择【任务管理器】选项。2、在打开的任务管理器界面,我们点击最右端的【服务】选项卡。3、在打开的【服务】选项卡,点击下方的【打开服务】选项。4、在打开的【服务】窗口,右击【InternetConnectionSharing(ICS)】服务,然后选择【属性】选项。5、在打开的属性窗口,将【打开方式】修改为【禁用】,点击【应用】后点击【确定】。6、点击开始徽标,然后点击关机按钮,选择【重启】,完成电脑重启就行了。

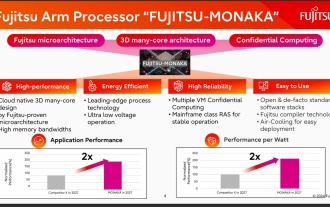

144 核心,3D 堆叠 SRAM:富士通详细介绍下一代数据中心处理器 MONAKA

Jul 29, 2024 am 11:40 AM

144 核心,3D 堆叠 SRAM:富士通详细介绍下一代数据中心处理器 MONAKA

Jul 29, 2024 am 11:40 AM

本站7月28日消息,据外媒TechRader报道,富士通详细介绍了计划于2027年出货的FUJITSU-MONAKA(以下简称MONAKA)处理器。MONAKACPU基于“云原生3D众核”架构,采用Arm指令集,面向数据中心、边缘与电信领域,适用于AI计算,能实现大型机级别的RAS1。富士通表示,MONAKA将在能效和性能方面实现飞跃:得益于超低电压(ULV)工艺等技术,该CPU可实现2027年竞品2倍的能效,冷却无需水冷;此外该处理器的应用性能也可达对手2倍。在指令方面,MONAKA配备的矢量