pcie3.0x4最大速度是多少

PCIe3.0x4理论最大读或者写的速度为4GB/s,不考虑协议开销,每秒可以传输4GB/4K个4K大小的IO,该值为1M,即理论上最大IOPS为1000K。因此,一个SSD不管底层用什么介质,flash还是3d xpoint,接口速度就这么块,最大IOPS是不可能超过这个值的。

本教程操作环境:windows7系统、Dell G3电脑。

PCIe接口介绍

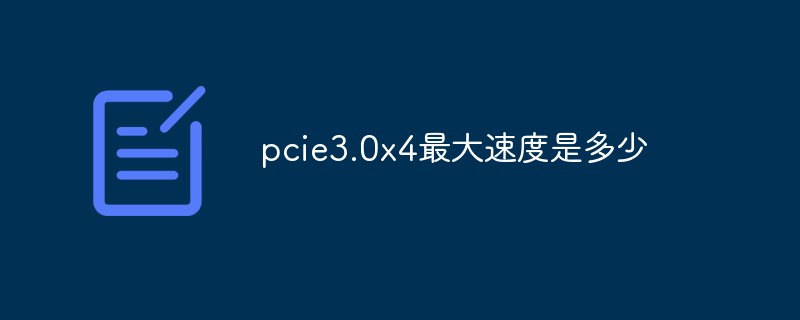

PCIe发展到现在,速度一代比一代快。

Link Width这一行,我们看到X1,X2,X4…,这是什么意思?这是指PCIe连接的通道数(Lane)。就像高速一样,有单根道,有2根道的,有4根道的,不过像8根道或者更多道的公路不常见,但PCIe是可以最多32条道的。

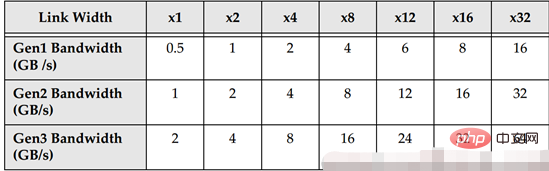

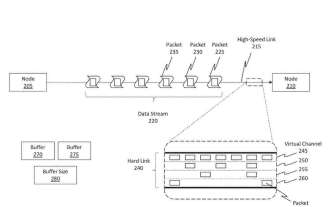

两个设备之间的PCIe连接,叫做一个Link,如下图所示:

从A到B,之间是个双向连接,车可以从A驶向B,同时,车也可以从B驶向A,各行其道。两个PCIe设备之间,有专门的发送和接收通道,数据可以同时往两个方向传输,PCIe spec称这种工作模式为双单工模式(dual-simplex),可以理解为全双工模式。

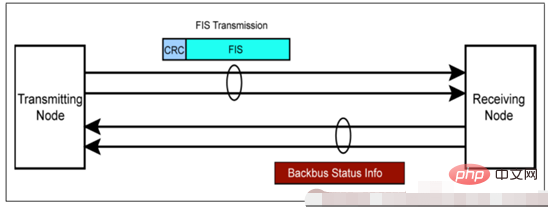

SATA是什么工作模式呢?

和PCIe一样,SATA也有独立的发送和接收通道,但与PCIe工作模式不一样:同一时间,只有一条道可以进行数据传输,也就是说,你在一条道上发送数据,另外一条道上不能接收数据,反之亦然。这种工作模式应该是半双工模式。PCIe犹如我们的手机,双方可以同时讲话,而SATA就是对讲机了,一个人在说话,另外一个人就只能听不能说。

回到前面PCIe带宽那张表,上面的带宽,比如PCIe3.0x1,带宽为2GB/s,是指双向带宽,即读写带宽。如果单指读或者写,该值应该减半,即1GB/s的读速度或者写速度。

我们来看看表里面的带宽是怎么算出来的。

PCIe是串行总线,PCIe1.0的线上比特传输速率为2.5Gb/s,物理层使用8/10编码,即8比特的数据,实际在物理线路上是需要传输10比特的,因此:

PCIe1.0 x 1的带宽=(2.5Gb/s x 2(双向通道))/ 10bit = 0.5GB/s

这是单条Lane的带宽,有几条Lane,那么整个带宽就0.5GB/s乘以Lane的数目。

PCIe2.0的线上比特传输速率在PCIe1.0的基础上翻了一倍,为5Gb/s,物理层同样使用8/10编码,所以:

PCIe2.0 x 1的带宽=(5Gb/s x 2(双向通道))/ 10bit = 1GB/s

同样,有多少条Lane,带宽就是1GB/s乘以Lane的数目。

PCIe3.0的线上比特传输速率没有在PCIe2.0的基础上翻倍,不是10Gb/s,而是8Gb/s,但物理层使用的是128/130编码进行数据传输,所以:

PCIe3.0 x 1的带宽=(8Gb/s x 2(双向通道))/ 8bit = 2GB/s

同样,有多少条Lane,带宽就是2GB/s乘以Lane的数目。

由于采用了128/130编码,128比特的数据,只额外增加了2bit的开销,有效数据传输比率增大,虽然线上比特传输率没有翻倍,但有效数据带宽还是在PCIe2.0的基础上做到翻倍。

这里值得一提的是,上面算出的数据带宽已经考虑到8/10或者128/130编码,因此,大家在算带宽的时候,没有必要再考虑线上编码的问题了。

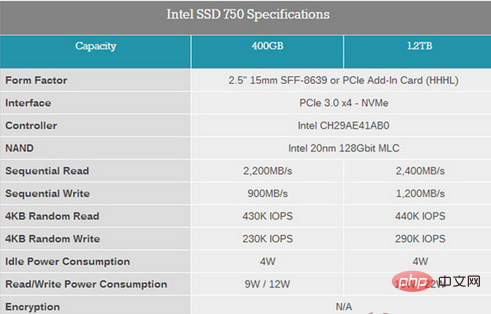

和SATA单通道不同,PCIe连接可以通过增加通道数扩展带宽,弹性十足。通道数越多,速度越快。不过,通道数越多,成本越高,占用更多空间,还有就是更耗电。因此,使用多少通道,应该在性能和其他因素之间进行一个综合考虑。单考虑性能的话,PCIe最高带宽可达64GB/s,PCIe 3.0 x 32对应的带宽,很恐怖的一个数据。不过,现有的PCIe接口SSD,一般最多使用4通道,如PCIe3.0x4,双向带宽为8GB/s,读或者写带宽为4GB/s。

几个GB/s的传输速度,读写小电影那是杠杠的。

在此,顺便来算算PCIe3.0x4理论上最大的4K IOPS。PCIe3.0x4理论最大读或者写的速度为4GB/s,不考虑协议开销,每秒可以传输4GB/4K个4K大小的IO,该值为1M,即理论上最大IOPS为1000K。因此,一个SSD,不管你底层用什么介质,flash还是3d xpoint,接口速度就这么块,最大IOPS是不可能超过这个值的。

PCIe是从PCI发展过来的,PCIe的”e”是express的简称,快的意思。PCIe怎么就能比PCI(或者PCI-X)快呢?PCIe在物理传输上,跟PCI有着本质的区别:PCI使用并口传输数据,而PCIe使用的是串口传输。我PCI并行总线,单个时钟周期可以传输32bit或者64bit,怎么就比不了你单个时钟周期传输1个bit数据的串行总线呢?

在实际时钟频率比较低的情况下,并口因为可以同时传输若干比特,速率确实比串口快。随着技术的发展,数据传输速率要求越来越快,要求时钟频率也越来越快,但是,并行总线时钟频率不是想快就能快的。

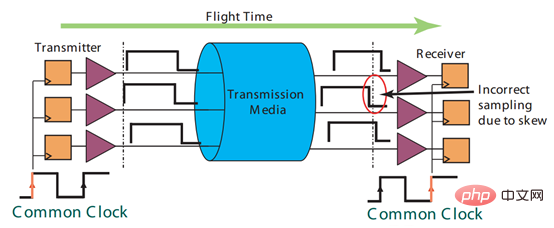

在发送端,数据在某个时钟沿传出去(左边时钟第一个上升沿),在接收端,数据在下个时钟沿(右边时钟第二个上升沿)接收。因此,要在接收端能正确采集到数据,要求时钟的周期必须大于数据传输的时间(从发送端到接收端,flight time)。受限于数据传输时间(该时间还随着数据线长度的增加而增加),因此时钟频率不能做得太高。另外,时钟信号在线上传输的时候,也会存在相位偏移(clock skew ),影响接收端的数据采集;还有,并行传输,接收端必须等最慢的那个bit数据到了以后,才能锁住整个数据 (signal skew)。

PCIe使用串行总线进行数据传输就没有这些问题。它没有外部时钟信号,它的时钟信息通过8/10编码或者128/130编码嵌入在数据流,接收端可以从数据流里面恢复时钟信息,因此,它不受数据在线上传输时间的限制,你导线多长都没有问题,你数据传输频率多快也没有问题;没有外部时钟信号,自然就没有所谓的clock skew问题;由于是串行传输,只有一个bit传输,所以不存在signal skew问题。但是,如果使用多条lane传输数据(串行中又有并行,哈哈),这个问题又回来了,因为接收端同样要等最慢的那个lane上的数据到达才能处理整个数据。

PCIe总线的基础知识

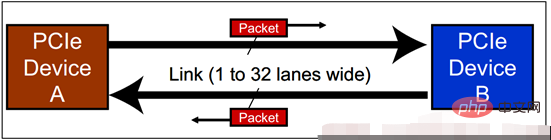

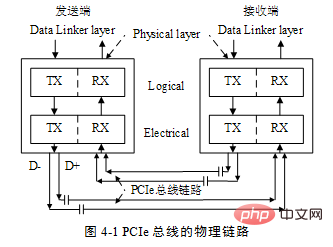

与PCI总线不同,PCIe总线使用端到端的连接方式,在一条PCIe链路的两端只能各连接一个设备,这两个设备互为是数据发送端和数据接收端。PCIe总线除了总线链路外,还具有多个层次,发送端发送数据时将通过这些层次,而接收端接收数据时也使用这些层次。PCIe总线使用的层次结构与网络协议栈较为类似。

PCIe链路使用“端到端的数据传送方式”,发送端和接收端中都含有TX(发送逻辑)和RX(接收逻辑),其结构如图所示。

由上图所示,在PCIe总线的物理链路的一个数据通路(Lane)中,由两组差分信号,共4根信号线组成。其中发送端的TX部件与接收端的RX部件使用一组差分信号连接,该链路也被称为发送端的发送链路,也是接收端的接收链路;而发送端的RX部件与接收端的TX部件使用另一组差分信号连接,该链路也被称为发送端的接收链路,也是接收端的发送链路。一个PCIe链路可以由多个Lane组成。

高速差分信号电气规范要求其发送端串接一个电容,以进行AC耦合。该电容也被称为AC耦合电容。PCIe链路使用差分信号进行数据传送,一个差分信号由D+和D-两根信号组成,信号接收端通过比较这两个信号的差值,判断发送端发送的是逻辑“1”还是逻辑“0”。

与单端信号相比,差分信号抗干扰的能力更强,因为差分信号在布线时要求“等长”、“等宽”、“贴近”,而且在同层。因此外部干扰噪声将被“同值”而且“同时”加载到D+和D-两根信号上,其差值在理想情况下为0,对信号的逻辑值产生的影响较小。因此差分信号可以使用更高的总线频率。

此外使用差分信号能有效抑制电磁干扰EMI(Electro Magnetic Interference)。由于差分信号D+与D-距离很近而且信号幅值相等、极性相反。这两根线与地线间耦合电磁场的幅值相等,将相互抵消,因此差分信号对外界的电磁干扰较小。当然差分信号的缺点也是显而易见的,一是差分信号使用两根信号传送一位数据;二是差分信号的布线相对严格一些。

PCIe链路可以由多条Lane组成,目前PCIe链路可以支持1、2、4、8、12、16和32个Lane,即×1、×2、×4、×8、×12、×16和×32宽度的PCIe链路。每一个Lane上使用的总线频率与PCIe总线使用的版本相关。

第1个PCIe总线规范为V1.0,之后依次为V1.0a,V1.1,V2.0和V2.1。目前PCIe总线的最新规范为V2.1,而V3.0正在开发过程中,预计在2010年发布。不同的PCIe总线规范所定义的总线频率和链路编码方式并不相同,如表41所示。

PCIe总线规范与总线频率和编码的关系

| PCIe总线规范 | 总线频率[1] | 单Lane的峰值带宽 | 编码方式 |

|---|---|---|---|

| 1.x | 1.25GHz | 2.5GT/s | 8/10b编码 |

| 2.x | 2.5GHz | 5GT/s | 8/10b编码 |

| 3.0 | 4GHz | 8GT/s | 128/130b编码 |

如上表所示,不同的PCIe总线规范使用的总线频率并不相同,其使用的数据编码方式也不相同。PCIe总线V1.x和V2.0规范在物理层中使用8/10b编码,即在PCIe链路上的10 bit中含有8 bit的有效数据;而V3.0规范使用128/130b编码方式,即在PCIe链路上的130 bit中含有128 bit的有效数据。

由上表所示,V3.0规范使用的总线频率虽然只有4GHz,但是其有效带宽是V2.x的两倍。下文将以V2.x规范为例,说明不同宽度PCIe链路所能提供的峰值带宽,如表42所示。

PCIe总线的峰值带宽

| PCIe总线的数据位宽 | ×1 | ×2 | ×4 | ×8 | ×12 | ×16 | ×32 |

|---|---|---|---|---|---|---|---|

| 峰值带宽(GT/s) | 5 | 10 | 20 | 40 | 60 | 80 | 160 |

由上表所示,×32的PCIe链路可以提供160GT/s的链路带宽,远高于PCI/PCI-X总线所能提供的峰值带宽。而即将推出的PCIe V3.0规范使用4GHz的总线频率,将进一步提高PCIe链路的峰值带宽。

在PCIe总线中,使用GT(Gigatransfer)计算PCIe链路的峰值带宽。GT是在PCIe链路上传递的峰值带宽,其计算公式为总线频率×数据位宽×2。

在PCIe总线中,影响有效带宽的因素有很多,因而其有效带宽较难计算。尽管如此,PCIe总线提供的有效带宽还是远高于PCI总线。PCIe总线也有其弱点,其中最突出的问题是传送延时。

PCIe链路使用串行方式进行数据传送,然而在芯片内部,数据总线仍然是并行的,因此PCIe链路接口需要进行串并转换,这种串并转换将产生较大的延时。除此之外PCIe总线的数据报文需要经过事务层、数据链路层和物理层,这些数据报文在穿越这些层次时,也将带来延时。

在基于PCIe总线的设备中,×1的PCIe链路最为常见,而×12的PCIe链路极少出现,×4和×8的PCIe设备也不多见。Intel通常在ICH中集成了多个×1的PCIe链路用来连接低速外设,而在MCH中集成了一个×16的PCIe链路用于连接显卡控制器。而PowerPC处理器通常能够支持×8、×4、×2和×1的PCIe链路。

PCIe总线物理链路间的数据传送使用基于时钟的同步传送机制,但是在物理链路上并没有时钟线,PCIe总线的接收端含有时钟恢复模块CDR(Clock Data Recovery),CDR将从接收报文中提取接收时钟,从而进行同步数据传递。

值得注意的是,在一个PCIe设备中除了需要从报文中提取时钟外,还使用了REFCLK+和REFCLK-信号对作为本地参考时钟

更多相关知识,请访问常见问题栏目!

以上是pcie3.0x4最大速度是多少的详细内容。更多信息请关注PHP中文网其他相关文章!

热AI工具

Undresser.AI Undress

人工智能驱动的应用程序,用于创建逼真的裸体照片

AI Clothes Remover

用于从照片中去除衣服的在线人工智能工具。

Undress AI Tool

免费脱衣服图片

Clothoff.io

AI脱衣机

AI Hentai Generator

免费生成ai无尽的。

热门文章

热工具

记事本++7.3.1

好用且免费的代码编辑器

SublimeText3汉化版

中文版,非常好用

禅工作室 13.0.1

功能强大的PHP集成开发环境

Dreamweaver CS6

视觉化网页开发工具

SublimeText3 Mac版

神级代码编辑软件(SublimeText3)

热门话题

请关闭电源并连接PCIe电源线

Feb 19, 2024 am 11:09 AM

请关闭电源并连接PCIe电源线

Feb 19, 2024 am 11:09 AM

如果您看到错误消息请关闭电源并连接Windows11/10PC上的PCIe电源线,请阅读此帖子以了解如何解决该问题。当PCIe设备(通常是图形卡)未能获得足够的电力时,可能会触发此错误。可能的原因包括PCIe电源线故障、连接问题或电源不足。若未正确连接电源线,则也可能导致此问题。请关闭电源并连接此显卡的PCIE电源线(S)初次使用个人电脑的用户或缺乏组装计算机系统经验的人经常会遇到这种问题。如果PCIe电缆因振动或时间推移而松动,也可能会导致该错误消息的出现。本文将介绍解决这一问题所需采取的步骤

pcie4.0和pcie3.0接口一样吗

Mar 13, 2023 pm 04:39 PM

pcie4.0和pcie3.0接口一样吗

Mar 13, 2023 pm 04:39 PM

pcie4.0和pcie3.0接口不一样,它们是两个不同版本的PCIe标准。两者的区别:1、PCIe4.0提供了更快的数据传输速度,高达16GT/s,是PCIe3.0的两倍;2、PCIe 4.0支持更多的带宽,最高可达69.6GB/s,而 PCIe3.0最高只能支持32GB/s;3、PCIe4.0支持更多的通道,可以支持更多的设备;4、PCIe4.0支持更低的电力消耗。

延迟 1 年,PCIe 6.0/7.0 规范部署遇阻碍

Jun 15, 2024 pm 04:45 PM

延迟 1 年,PCIe 6.0/7.0 规范部署遇阻碍

Jun 15, 2024 pm 04:45 PM

本站6月15日消息,外设组件互连特别兴趣小组(PCI-SIG)本周召开举办2024开发者大会,公布了PCIe6.0和PCIe7.0的最新进展情况,表示上述两个标准虽然已取得一定进展,但部署普及时间要比预期要慢。PCI-SIG目前已经推迟启动“一致性计划”(ComplianceProgram),PCIe6.0的初步一致性测试原定于今年3月开始,目前已经推迟到“第2季度”,也就是会在本月底前测试。2023年(上)和2024年(下)的PCIe标准发布路线图该机构表示PCIe6.0深度一致性测试将于20

pcie3.0x4最大速度是多少

Mar 15, 2023 pm 05:09 PM

pcie3.0x4最大速度是多少

Mar 15, 2023 pm 05:09 PM

PCIe3.0x4理论最大读或者写的速度为4GB/s,不考虑协议开销,每秒可以传输4GB/4K个4K大小的IO,该值为1M,即理论上最大IOPS为1000K。因此,一个SSD不管底层用什么介质,flash还是3d xpoint,接口速度就这么块,最大IOPS是不可能超过这个值的。

PCIe 7.0 规范正式初稿(0.5 版本)公布,仍有望于明年全面发布

Apr 04, 2024 am 08:37 AM

PCIe 7.0 规范正式初稿(0.5 版本)公布,仍有望于明年全面发布

Apr 04, 2024 am 08:37 AM

本站4月3日消息,PCIe规范制定组织PCI-SIG近日宣布PCIe7.0规范的0.5版本,也就是其正式初稿现已向PCI-SIG成员公布。相较于2022年初发布的PCIe6.0规范,PCIe7.0规范在沿用PAM4信号调制方式的同时再次翻倍速率,可实现128GT/s的原始数据速率,并在x16配置下实现512GB/s的双向比特率。PCIe7.0架构的开发重点是提升信道参数、覆盖范围和能源效率,旨在为800G以太网、AI/ML工作负载,超大规模数据中心、高性能计算、量子计算、云等数据密集型应用提供可

2024 年科隆游戏展 |华硕和微星揭示 GPU 和 M.2 SSD 的创新快速释放机制

Aug 25, 2024 am 06:30 AM

2024 年科隆游戏展 |华硕和微星揭示 GPU 和 M.2 SSD 的创新快速释放机制

Aug 25, 2024 am 06:30 AM

在 Gamescom 2024 上,华硕和 MSI 推出了一些很酷的 GPU 和 M.2 SSD 快速释放机制,确实引人注目。这些新功能旨在让构建 PC 的人们的生活变得更轻松,尤其是在处理那些笨重的组件时。华硕罗勒

改进HoloLens内部PCIe数据链接传输:微软分享AR/VR专利

Jan 03, 2024 pm 02:05 PM

改进HoloLens内部PCIe数据链接传输:微软分享AR/VR专利

Jan 03, 2024 pm 02:05 PM

(映维网Nweon2023年12月27日)有线连接通常称为“硬链接”,它将一个节点物理地连接到另一个节点。一种有线连接是PCIe。PCIe是一种用于连接高速节点的接口,而尽管诸如PCIe等高速连接终端和协议提供了实质性的优势,但所述类型的终端需要高功率运行。对于头显这样的电池供电计算架构,这会给系统带来巨大的负担。在名为“Errorrecoveryandpowermanagementbetweennodesofaninterconnectionnetwork”的专利申请中,微软介绍了通过从错误条

PCIe 6 发热咋办?英特尔提交新驱动,通过控制总线速度缓解

Jun 04, 2024 am 10:28 AM

PCIe 6 发热咋办?英特尔提交新驱动,通过控制总线速度缓解

Jun 04, 2024 am 10:28 AM

本站5月11日消息,PCIe版本更迭带来了更高的带宽、更快的传输速度,同时也带来了更多的热量。英特尔公司近日发布Linux驱动程序,通过开源的“PCIe带宽控制器”来遏制热量,在热量达到一定阈值时自动控制链路速度。本站注:PCIe版本更迭不仅提高了传输速度,还要求更好的信号完整性和更低的信号损耗,因此往往需要更高的时钟频率、更大的功率和编码优化,而所有这些都会产生额外的热量。英特尔工程师IlpoJärvinen在最新的补丁说明中写道:“该系列补丁仅增加了对控制PCIe链路速度的支持。控制PCIe